### **MSI Core Business**

License Pix2Net Software

Suite

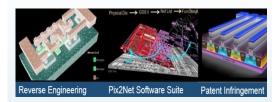

State of the Art IC Reverse

Engineering

Electronic Part

Obsolescence

Trusted system/Cyber

Vulnerability

Anti-Tamper Design & Analysis

*IC Patent Infringement*

## MicroNet Solutions Inc.

10501 Research Rd. SE Suite C Albuquerque, NM 87123 Phone: 505.765.2498 www.micronetsol.net

E-mail: mstriz@micronetsol.net

## Pix2Net

# Software Suite

MSI Newsletter - Oct. 2014

Pix2Net Software Suite...... For Rapid Reverse Engineering of Microelectronics

#### Pix2Net Software Solutions

Michael Strizich, President MSI Oct. 2014

# The Solution..... MicroNet Solutions Inc. (MSI)

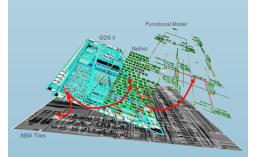

has developed proprietary techniques, and software to reverse engineer complex microcircuits and systems, allowing for complete extraction of functionality and microcode. Reverse Engineering state-of-the art microchips is very difficult at best given the small dimensions, density of transistors and number of metal layers (Billions of nodes of information to track).

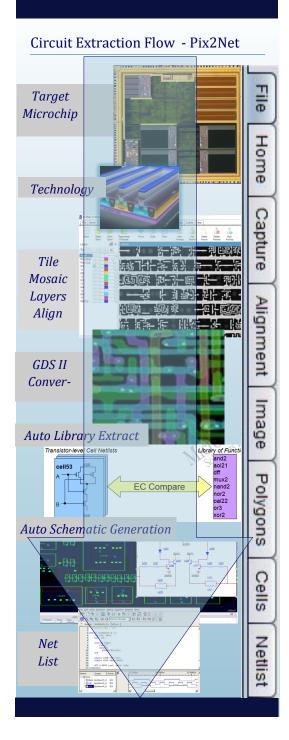

The Pix2Net software suite features a proprietary software guided stage allowing for accurate SEM tile extraction, and stitching for perfect layer alignment. The GDSII extracted conductive layers are accurately stacked and aligned for circuit connection.

#### From Pixtures 2 Net Lists

#### The MicroNet Solution.....

The MSI Team has over 25 years experience focused on rapid, state-of-the art reverse engineering of complex integrated circuits . The cost effective solutions starts with MSI's Nanostage which is used for the capture and stitching of images using proprietary software to form a continuous mosaic layer. This novel Nano-stage can be interfaced with most modern SEM's .

Pix2Net Nano-Stage

The continuous mosaic layers are accurately stacked and aligned for circuit connection. They are then converted to GDSII to reveal each lithographic layer. Subsequently, the digital and analog library cells are automatically extracted using MSI 's proprietary software which performs transistor level net listing in conjunction with a reference functional database containing Verilog, VHDL and SPICE models. The library cell instances are discovered and placed using proprietary pattern recognition algorithms.

Completed Net lists, Models, and GDS II files can be exported to the most common IC chip design software applications to complete the process.